# **EEPROM Serial 64-Kb SPI Automotive Grade 1**

## **CAV25640**

#### **Description**

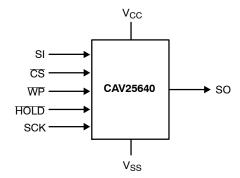

The CAV25640 is a EEPROM Serial 64–Kb SPI Automotive Grade 1 device internally organized as 8Kx8 bits. This features a 64–byte page write buffer and supports the Serial Peripheral Interface (SPI) protocol. The device is enabled through a Chip Select  $(\overline{CS})$  input. In addition, the required bus signals are clock input (SCK), data input (SI) and data output (SO) lines. The  $\overline{HOLD}$  input may be used to pause any serial communication with the CAV25640 device. The device features software and hardware write protection, including partial as well as full array protection.

#### **Features**

- Automotive AEC-Q100 Grade 1 (-40°C to +125°C) Qualified

- 10 MHz SPI Compatible

- 2.5 V to 5.5 V Supply Voltage Range

- SPI Modes (0,0) & (1,1)

- 64-byte Page Write Buffer

- Self-timed Write Cycle

- Hardware and Software Protection

- CAV Prefix for Automotive and Other Applications Requiring Site and Change Control

- Block Write Protection

- Protect <sup>1</sup>/<sub>4</sub>, <sup>1</sup>/<sub>2</sub> or Entire EEPROM Array

- Low Power CMOS Technology

- 1,000,000 Program/Erase Cycles

- 100 Year Data Retention

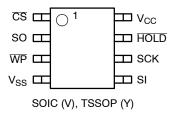

- SOIC and TSSOP 8-lead Packages

- This Device is Pb–Free, Halogen Free/BFR Free, and RoHS Compliant

Figure 1. Functional Symbol

TSSOP-8 Y SUFFIX CASE 948AL

#### **PIN CONFIGURATION**

#### **PIN FUNCTION**

| Pin Name        | Function                |  |

|-----------------|-------------------------|--|

| CS              | Chip Select             |  |

| so              | Serial Data Output      |  |

| WP              | Write Protect           |  |

| V <sub>SS</sub> | Ground                  |  |

| SI              | Serial Data Input       |  |

| SCK             | Serial Clock            |  |

| HOLD            | Hold Transmission Input |  |

| V <sub>CC</sub> | Power Supply            |  |

#### ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 10 of this data sheet.

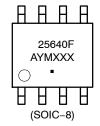

#### **MARKING DIAGRAMS**

25640F = Specific Device Code

= Assembly Location

= Production Year (Last Digit)

= Production Month (1-9, O, N, D) М

XXX = Last Three Digits of Assembly Lot Number

= Pb-Free Package

S64F = Specific Device Code

= Assembly Location

= Production Year (Last Digit)

М = Production Month (1-9, O, N, D)

XXX = Last Three Digits of

Assembly Lot Number

= Pb-Free Package

#### **Table 1. ABSOLUTE MAXIMUM RATINGS**

| Parameters                                         | Ratings      | Units |

|----------------------------------------------------|--------------|-------|

| Operating Temperature                              | -45 to +130  | °C    |

| Storage Temperature                                | -65 to +150  | °C    |

| Voltage on any Pin with Respect to Ground (Note 1) | -0.5 to +6.5 | V     |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. The DC input voltage on any pin should not be lower than -0.5 V or higher than V<sub>CC</sub> + 0.5 V. During transitions, the voltage on any pin may undershoot to no less than -1.5 V or overshoot to no more than  $V_{CC} + 1.5$  V, for periods of less than 20 ns.

#### Table 2. RELIABILITY CHARACTERISTICS (Note 2)

| Symbol                    | Parameter      | Min       | Units                  |

|---------------------------|----------------|-----------|------------------------|

| N <sub>END</sub> (Note 3) | Endurance      | 1,000,000 | Program / Erase Cycles |

| T <sub>DR</sub>           | Data Retention | 100       | Years                  |

These parameters are tested initially and after a design or process change that affects the parameter according to appropriate AEC-Q100 and JEDEC test methods.

Table 3. D.C. OPERATING CHARACTERISTICS (V<sub>CC</sub> = 2.5 V to 5.5 V, T<sub>A</sub> = -40°C to +125°C, unless otherwise specified.)

| Symbol           | Parameter                   | Test Conditions                                                                                                | Min                     | Max                   | Units |

|------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------|-------|

| I <sub>CCR</sub> | Supply Current (Read Mode)  | Read, V <sub>CC</sub> = 5.5 V, 5 MHz, SO open                                                                  |                         | 2                     | mA    |

| I <sub>CCW</sub> | Supply Current (Write Mode) | Write, V <sub>CC</sub> = 5.5 V, 5 MHz, SO open                                                                 |                         | 3                     | mA    |

| I <sub>SB1</sub> | Standby Current             | $V_{IN} = GND \text{ or } V_{CC}, \overline{CS} = V_{CC},$<br>$\overline{WP} = V_{CC}, V_{CC} = 5.5 \text{ V}$ |                         | 2                     | μΑ    |

| I <sub>SB2</sub> | Standby Current             | $V_{IN} = GND \text{ or } V_{CC}, \overline{CS} = V_{CC},$<br>$\overline{WP} = GND, V_{CC} = 5.5 \text{ V}$    |                         | 5                     | μΑ    |

| ΙL               | Input Leakage Current       | V <sub>IN</sub> = GND or V <sub>CC</sub>                                                                       | -2                      | 2                     | μΑ    |

| I <sub>LO</sub>  | Output Leakage Current      | CS = V <sub>CC</sub> ,<br>V <sub>OUT</sub> = GND or V <sub>CC</sub>                                            | -1                      | 2                     | μΑ    |

| V <sub>IL</sub>  | Input Low Voltage           |                                                                                                                | -0.5                    | 0.3 V <sub>CC</sub>   | ٧     |

| V <sub>IH</sub>  | Input High Voltage          |                                                                                                                | 0.7 V <sub>CC</sub>     | V <sub>CC</sub> + 0.5 | ٧     |

| V <sub>OL1</sub> | Output Low Voltage          | I <sub>OL</sub> = 3.0 mA                                                                                       |                         | 0.4                   | V     |

| V <sub>OH1</sub> | Output High Voltage         | I <sub>OH</sub> = -1.6 mA                                                                                      | V <sub>CC</sub> – 0.8 V |                       | V     |

<sup>3.</sup> Page Mode,  $V_{CC} = 5 \text{ V}$ ,  $25^{\circ}\text{C}$ .

Table 4. PIN CAPACITANCE ( $T_A = 25^{\circ}C$ , f = 1.0 MHz,  $V_{CC} = +5.0$  V) (Note 2)

| Symbol           | Test                                      | Conditions             | Min | Тур | Max | Units |

|------------------|-------------------------------------------|------------------------|-----|-----|-----|-------|

| C <sub>OUT</sub> | Output Capacitance (SO)                   | V <sub>OUT</sub> = 0 V |     |     | 8   | pF    |

| C <sub>IN</sub>  | Input Capacitance (CS, SCK, SI, WP, HOLD) | V <sub>IN</sub> = 0 V  |     |     | 8   | pF    |

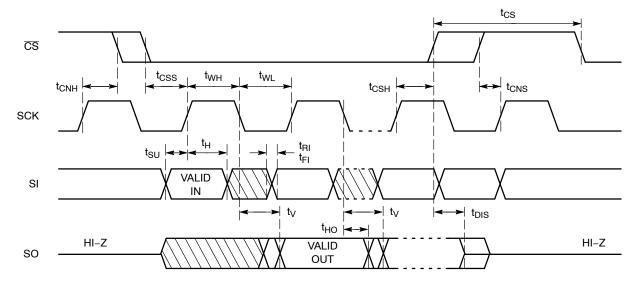

Table 5. A.C. CHARACTERISTICS ( $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ ) (Note 4)

|                          |                             | V <sub>CC</sub> = 2.5 | V – 5.5 V |       |

|--------------------------|-----------------------------|-----------------------|-----------|-------|

| Symbol                   | Parameter                   | Min                   | Max       | Units |

| f <sub>SCK</sub>         | Clock Frequency             | DC                    | 10        | MHz   |

| t <sub>SU</sub>          | Data Setup Time             | 10                    |           | ns    |

| t <sub>H</sub>           | Data Hold Time              | 10                    |           | ns    |

| t <sub>WH</sub>          | SCK High Time               | 40                    |           | ns    |

| t <sub>WL</sub>          | SCK Low Time                | 40                    |           | ns    |

| t <sub>LZ</sub>          | HOLD to Output Low Z        |                       | 25        | ns    |

| t <sub>RI</sub> (Note 5) | Input Rise Time             |                       | 2         | μs    |

| t <sub>FI</sub> (Note 5) | Input Fall Time             |                       | 2         | μs    |

| t <sub>HD</sub>          | HOLD Setup Time             | 0                     |           | ns    |

| t <sub>CD</sub>          | HOLD Hold Time              | 10                    |           | ns    |

| t <sub>V</sub>           | Output Valid from Clock Low |                       | 35        | ns    |

| t <sub>HO</sub>          | Output Hold Time            | 0                     |           | ns    |

| t <sub>DIS</sub>         | Output Disable Time         |                       | 20        | ns    |

| t <sub>HZ</sub>          | HOLD to Output High Z       |                       | 25        | ns    |

| t <sub>CS</sub>          | CS High Time                | 40                    |           | ns    |

| t <sub>CSS</sub>         | CS Setup Time               | 30                    |           | ns    |

| t <sub>CSH</sub>         | CS Hold Time                | 30                    |           | ns    |

| t <sub>CNS</sub>         | CS Inactive Setup Time      | 20                    |           | ns    |

| t <sub>CNH</sub>         | CS Inactive Hold Time       | 20                    |           | ns    |

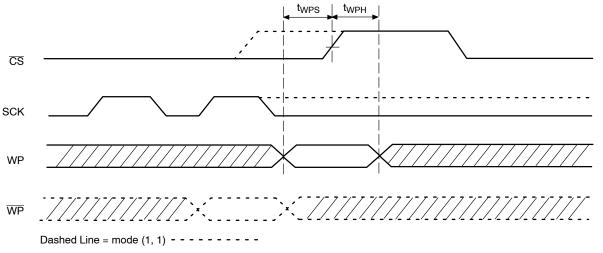

| t <sub>WPS</sub>         | WP Setup Time               | 10                    |           | ns    |

| t <sub>WPH</sub>         | WP Hold Time                | 10                    |           | ns    |

| t <sub>WC</sub> (Note 6) | Write Cycle Time            |                       | 5         | ms    |

#### 4. AC Test Conditions:

Input Pulse Voltages: 0.3 V<sub>CC</sub> to 0.7 V<sub>CC</sub> Input rise and fall times: ≤ 10 ns

- Input and output reference voltages: 0.5 V<sub>CC</sub>

Output load: current source I<sub>OL max</sub>/I<sub>OH max</sub>; C<sub>L</sub> = 30 pF

5. This parameter is tested initially and after a design or process change that affects the parameter.

6. t<sub>WC</sub> is the time from the rising edge of CS after a valid write sequence to the end of the internal write cycle.

### Table 6. POWER-UP TIMING (Notes 5, 7)

| Symbol           | Symbol Parameter                            |   | Units |

|------------------|---------------------------------------------|---|-------|

| t <sub>PUR</sub> | t <sub>PUR</sub> Power-up to Read Operation |   | ms    |

| t <sub>PUW</sub> | Power-up to Write Operation                 | 1 | ms    |

<sup>7.</sup> t<sub>PUR</sub> and t<sub>PUW</sub> are the delays required from the time V<sub>CC</sub> is stable until the specified operation can be initiated.

#### **Pin Description**

SI: The serial data input pin accepts op-codes, addresses and data. In SPI modes (0,0) and (1,1) input data is latched on the rising edge of the SCK clock input.

**SO:** The serial data output pin is used to transfer data out of the device. In SPI modes (0,0) and (1,1) data is shifted out on the falling edge of the SCK clock.

**SCK:** The serial clock input pin accepts the clock provided by the host and used for synchronizing communication between host and CAV25640.

$\overline{\text{CS}}$ : The chip select input pin is used to enable/disable the CAV25640. When  $\overline{\text{CS}}$  is high, the SO output is tri-stated (high impedance) and the device is in Standby Mode (unless an internal write operation is in progress). Every communication session between host and CAV25640 must be preceded by a high to low transition and concluded with a low to high transition of the  $\overline{\text{CS}}$  input.

$\overline{\mathbf{WP}}$ : The write protect input pin will allow all write operations to the device when held high. When  $\overline{\mathbf{WP}}$  pin is tied low and the WPEN bit in the Status Register (refer to Status Register description, later in this Data Sheet) is set to "1", writing to the Status Register is disabled.

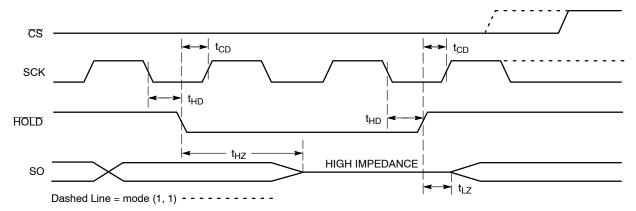

$\overline{\text{HOLD}}$ : The  $\overline{\text{HOLD}}$  input pin is used to pause transmission between host and CAV25640, without having to retransmit the entire sequence at a later time. To pause,  $\overline{\text{HOLD}}$  must be taken low and to resume it must be taken back high, with the SCK input low during both transitions. When not used for pausing, the  $\overline{\text{HOLD}}$  input should be tied to  $V_{CC}$ , either directly or through a resistor.

#### **Functional Description**

The CAV25640 device supports the Serial Peripheral Interface (SPI) bus protocol, modes (0,0) and (1,1). The device contains an 8-bit instruction register. The instruction set and associated op-codes are listed in Table 7.

Reading data stored in the CAV25640 is accomplished by simply providing the READ command and an address. Writing to the CAV25640, in addition to a WRITE command, address and data, also requires enabling the device for writing by first setting certain bits in a Status Register, as will be explained later.

After a high to low transition on the  $\overline{\text{CS}}$  input pin, the CAV25640 will accept any one of the six instruction op-codes listed in Table 7 and will ignore all other possible 8-bit combinations. The communication protocol follows the timing from Figure 2.

**Table 7. INSTRUCTION SET**

| Instruction | Op-code   | Operation                |

|-------------|-----------|--------------------------|

| WREN        | 0000 0110 | Enable Write Operations  |

| WRDI        | 0000 0100 | Disable Write Operations |

| RDSR        | 0000 0101 | Read Status Register     |

| WRSR        | 0000 0001 | Write Status Register    |

| READ        | 0000 0011 | Read Data from Memory    |

| WRITE       | 0000 0010 | Write Data to Memory     |

Figure 2. Synchronous Data Timing

#### **Status Register**

The Status Register, as shown in Table 8, contains a number of status and control bits.

The RDY (Ready) bit indicates whether the device is busy with a write operation. This bit is automatically set to 1 during an internal write cycle, and reset to 0 when the device is ready to accept commands. For the host, this bit is read only.

The WEL (Write Enable Latch) bit is set/reset by the WREN/WRDI commands. When set to 1, the device is in a Write Enable state and when set to 0, the device is in a Write Disable state.

The BP0 and BP1 (Block Protect) bits determine which blocks are currently write protected. They are set by the user with the WRSR command and are non-volatile. The user is

allowed to protect a quarter, one half or the entire memory, by setting these bits according to Table 9. The protected blocks then become read—only.

The WPEN (Write Protect Enable) bit acts as an enable for the  $\overline{WP}$  pin. Hardware write protection is enabled when the  $\overline{WP}$  pin is low and the WPEN bit is 1. This condition prevents writing to the status register and to the block protected sections of memory. While hardware write protection is active, only the non-block protected memory can be written. Hardware write protection is disabled when the  $\overline{WP}$  pin is high or the WPEN bit is 0. The WPEN bit,  $\overline{WP}$  pin and WEL bit combine to either permit or inhibit Write operations, as detailed in Table 10.

**Table 8. STATUS REGISTER**

| 7    | 6 | 5 | 4 | 3   | 2   | 1   | 0   |

|------|---|---|---|-----|-----|-----|-----|

| WPEN | 0 | 0 | 0 | BP1 | BP0 | WEL | RDY |

**Table 9. BLOCK PROTECTION BITS**

| Status Re | gister Bits |                         |                          |

|-----------|-------------|-------------------------|--------------------------|

| BP1       | BP0         | Array Address Protected | Protection               |

| 0         | 0           | None                    | No Protection            |

| 0         | 1           | 1800-1FFF               | Quarter Array Protection |

| 1         | 0           | 1000-1FFF               | Half Array Protection    |

| 1         | 1           | 0000-1FFF               | Full Array Protection    |

#### **Table 10. WRITE PROTECT CONDITIONS**

| WPEN | WP   | WEL | Protected Blocks | Unprotected Blocks | Status Register |

|------|------|-----|------------------|--------------------|-----------------|

| 0    | Х    | 0   | Protected        | Protected          | Protected       |

| 0    | Х    | 1   | Protected        | Writable           | Writable        |

| 1    | Low  | 0   | Protected        | Protected          | Protected       |

| 1    | Low  | 1   | Protected        | Writable           | Protected       |

| Х    | High | 0   | Protected        | Protected          | Protected       |

| X    | High | 1   | Protected        | Writable           | Writable        |

#### WRITE OPERATIONS

The CAV25640 device powers up into a write disable state. The device contains a Write Enable Latch (WEL) which must be set before attempting to write to the memory array or to the status register. In addition, the address of the memory location(s) to be written must be outside the protected area, as defined by BP0 and BP1 bits from the status register.

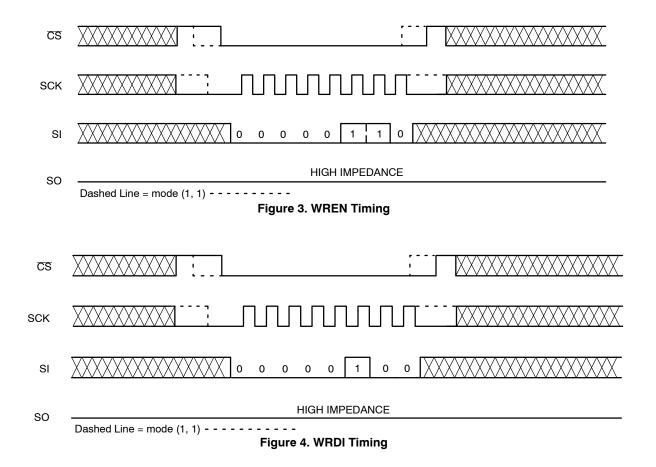

#### Write Enable and Write Disable

The internal Write Enable Latch and the corresponding Status Register WEL bit are set by sending the WREN instruction to the CAV25640. Care must be taken to take the  $\overline{\text{CS}}$  input high after the WREN instruction, as otherwise the Write Enable Latch will not be properly set. WREN timing is illustrated in Figure 3. The WREN instruction must be sent prior to any WRITE or WRSR instruction.

The internal write enable latch is reset by sending the WRDI instruction as shown in Figure 4. Disabling write operations by resetting the WEL bit, will protect the device against inadvertent writes.

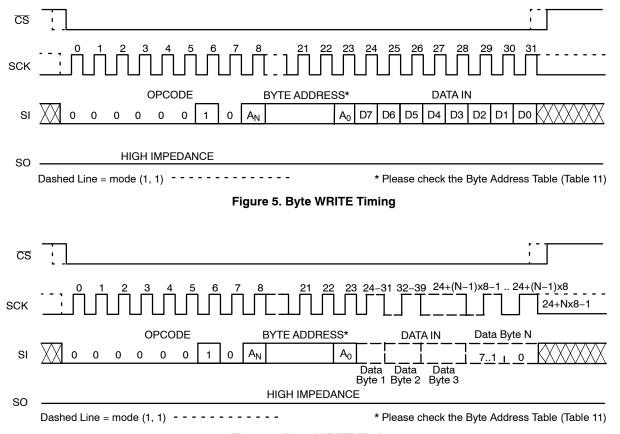

### **Byte Write**

Once the WEL bit is set, the user may execute a write sequence, by sending a WRITE instruction, a 16-bit address and data as shown in Figure 5. Only 13 significant address bits are used by the CAV25640. The rest are don't care bits, as shown in Table 11. Internal programming will start after the low to high  $\overline{\text{CS}}$  transition. During an internal write cycle, all commands, except for RDSR (Read Status Register) will be ignored. The  $\overline{\text{RDY}}$  bit will indicate if the internal write cycle is in progress ( $\overline{\text{RDY}}$  high), or the device is ready to accept commands ( $\overline{\text{RDY}}$  low).

#### **Page Write**

After sending the first data byte to the CAV25640, the host may continue sending data, up to a total of 64 bytes, according to timing shown in Figure 6. After each data byte, the lower order address bits are automatically incremented, while the higher order address bits (page address) remain unchanged. If during this process the end of page is exceeded, then loading will "roll over" to the first byte in the page, thus possibly overwriting previously loaded data. Following completion of the write cycle, the CAV25640 is automatically returned to the write disable state.

**Table 11. BYTE ADDRESS**

| Device   | Address Significant Bits | Address Don't Care Bits | # Address Clock Pulses |

|----------|--------------------------|-------------------------|------------------------|

| CAV25640 | A12 – A0                 | A15 – A13               | 16                     |

Figure 6. Page WRITE Timing

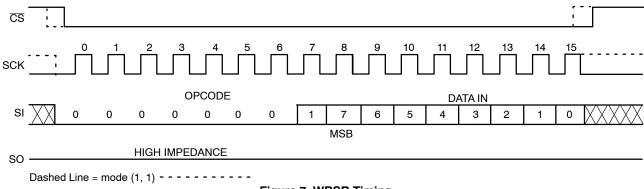

#### Write Status Register

The Status Register is written by sending a WRSR instruction according to timing shown in Figure 7. Only bits 2, 3 and 7 can be written using the WRSR command.

#### **Write Protection**

The Write Protect  $(\overline{WP})$  pin can be used to protect the Block Protect bits BP0 and BP1 against being inadvertently altered. When  $\overline{WP}$  is low and the WPEN bit is set to "1", write operations to the Status Register are inhibited.  $\overline{WP}$  going low while  $\overline{CS}$  is still low will interrupt a write to the status register. If the internal write cycle has already been initiated,  $\overline{WP}$  going low will have no effect on any write operation to the Status Register. The  $\overline{WP}$  pin function is blocked when the WPEN bit is set to "0". The  $\overline{WP}$  input timing is shown in Figure 8.

Figure 7. WRSR Timing

Figure 8. WP Timing

#### **READ OPERATIONS**

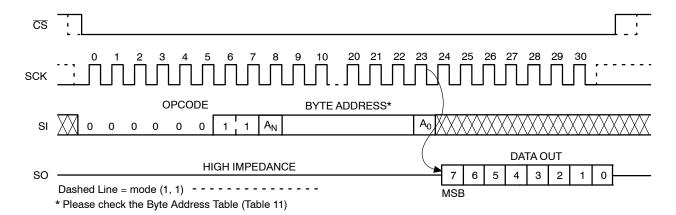

#### **Read from Memory Array**

To read from memory, the host sends a READ instruction followed by a 16-bit address (see Table 11 for the number of significant address bits).

After receiving the last address bit, the CAV25640 will respond by shifting out data on the SO pin (as shown in Figure 9). Sequentially stored data can be read out by simply continuing to run the clock. The internal address pointer is automatically incremented to the next higher address as data is shifted out. After reaching the highest memory address, the address counter "rolls over" to the lowest memory

address, and the read cycle can be continued indefinitely. The read operation is terminated by taking  $\overline{CS}$  high.

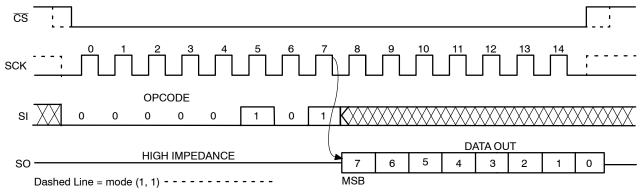

#### **Read Status Register**

To read the status register, the host simply sends a RDSR command. After receiving the last bit of the command, the CAV25640 will shift out the contents of the status register on the SO pin (Figure 10). The status register may be read at any time, including during an internal write cycle. While the internal write cycle is in progress, the RDSR command will output the contents of the status register.

Figure 9. READ Timing

Figure 10. RDSR Timing

#### **Hold Operation**

The HOLD input can be used to pause communication between host and CAV25640. To pause, HOLD must be taken low while SCK is low (Figure 11). During the hold condition the device must remain selected (CS low). During the pause, the data output pin (SO) is tri-stated (high impedance) and SI transitions are ignored. To resume communication, HOLD must be taken high while SCK is low.

#### **Design Considerations**

The CAV25640 device incorporates Power–On Reset (POR) circuitry which protects the internal logic against powering up in the wrong state. The device will power up into Standby mode after  $V_{\rm CC}$  exceeds the POR trigger level and will power down into Reset mode when  $V_{\rm CC}$  drops

below the POR trigger level. This bi-directional POR behavior protects the device against 'brown-out' failure following a temporary loss of power.

The CAV25640 device powers up in a write disable state and in a low power standby mode. A WREN instruction must be issued prior to any writes to the device.

After power up, the  $\overline{\text{CS}}$  pin must be brought low to enter a ready state and receive an instruction. After a successful byte/page write or status register write, the device goes into a write disable mode. The  $\overline{\text{CS}}$  input must be set high after the proper number of clock cycles to start the internal write cycle. Access to the memory array during an internal write cycle is ignored and programming is continued. Any invalid op–code will be ignored and the serial output pin (SO) will remain in the high impedance state.

Figure 11. HOLD Timing

#### **ORDERING INFORMATION** (Notes 8 - 10)

| Device Order Number | Specific Device Marking | Package Type         | Shipping <sup>†</sup> |

|---------------------|-------------------------|----------------------|-----------------------|

| CAV25640VE-GT3      | 25640F                  | SOIC-8<br>(Pb-Free)  | 3,000 / Tape & Reel   |

| CAV25640YE-GT3      | S64F                    | TSSOP-8<br>(Pb-Free) | 3,000 / Tape & Reel   |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

<sup>8.</sup> All packages are RoHS-compliant (Lead-free, Halogen-free).

<sup>9.</sup> The standard lead finish is NiPdAu.

<sup>10.</sup> For additional package and temperature options, please contact your nearest onsemi Sales office.

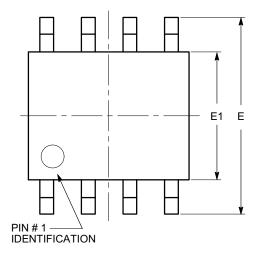

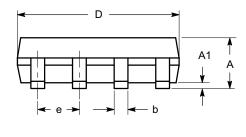

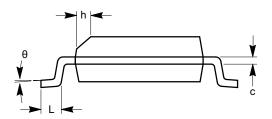

SOIC 8, 150 mils CASE 751BD-01 ISSUE O

**DATE 19 DEC 2008**

| SYMBOL | MIN  | NOM      | MAX  |

|--------|------|----------|------|

| Α      | 1.35 |          | 1.75 |

| A1     | 0.10 |          | 0.25 |

| b      | 0.33 |          | 0.51 |

| С      | 0.19 |          | 0.25 |

| D      | 4.80 |          | 5.00 |

| Е      | 5.80 |          | 6.20 |

| E1     | 3.80 |          | 4.00 |

| е      |      | 1.27 BSC |      |

| h      | 0.25 |          | 0.50 |

| L      | 0.40 |          | 1.27 |

| θ      | 0°   |          | 8°   |

**TOP VIEW**

SIDE VIEW

**END VIEW**

#### Notes:

- (1) All dimensions are in millimeters. Angles in degrees.

- (2) Complies with JEDEC MS-012.

| DOCUMENT NUMBER: | 98AON34272E      | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | SOIC 8, 150 MILS |                                                                                                                                                                                     | PAGE 1 OF 1 |

ON Semiconductor and (III) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

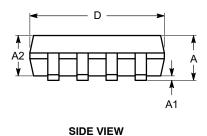

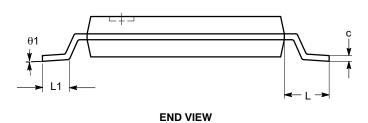

TSSOP8, 4.4x3 CASE 948AL-01 ISSUE O

**DATE 19 DEC 2008**

| SYMBOL | MIN      | NOM  | MAX  |

|--------|----------|------|------|

| Α      |          |      | 1.20 |

| A1     | 0.05     |      | 0.15 |

| A2     | 0.80     | 0.90 | 1.05 |

| b      | 0.19     |      | 0.30 |

| С      | 0.09     |      | 0.20 |

| D      | 2.90     | 3.00 | 3.10 |

| Е      | 6.30     | 6.40 | 6.50 |

| E1     | 4.30     | 4.40 | 4.50 |

| е      | 0.65 BSC |      |      |

| L      | 1.00 REF |      |      |

| L1     | 0.50     | 0.60 | 0.75 |

| θ      | 0°       |      | 8°   |

#### Notes:

- (1) All dimensions are in millimeters. Angles in degrees.

- (2) Complies with JEDEC MO-153.

| DOCUMENT NUMBER: | 98AON34428E   | Electronic versions are uncontrolled except when accessed directly from the Document Repository<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | TSSOP8, 4.4X3 |                                                                                                                                                                                    | PAGE 1 OF 1 |

ON Semiconductor and III are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

LITERATURE FULFILLMENT: Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

**TECHNICAL SUPPORT** North American Technical Support: Voice Mail: 1 800–282–9855 Toll Free USA/Canada

Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

## onsemi